# **Automotive uPOL MODUL**

VUN12AD03-KM

# 3A, High Efficiency uPOL Module

#### **FEATURES:**

- High Density Fully Integration Module

- Maximum Output Current: 3A

- Input Voltage Range from 4V to 36V

- Output Voltage Range from 0.9V to 8V

- VIN Maximum Rating 42V

- Switching Frequency 430kHz

- Approaching 100% duty cycle

- Selectable PSM/FPWM at Light Load

- Enable Function

- Protections (UVLO, OTP, OCP:non-latching)

- Power Good Indicator

- Selectable Spread Spectrum Frequency

- Wettable Flank Packaging

- Compact Size: 6mm\*6mm\*3.5mm

- Pb-free for RoHS compliant

- MSL 2, 260C Reflow

- AECQ-100 certificate

#### **GENERAL DESCRIPTION:**

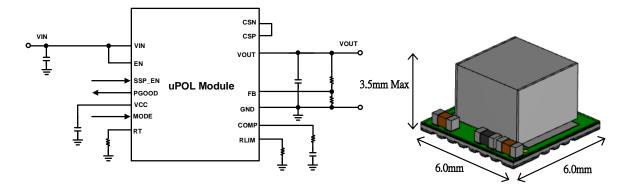

The uPOL Module is non-isolated dc-dc converter that can deliver up to 3A. The PWM switching regulator and high frequency power inductor are integrated in one hybrid package.

Some features can be adjusted by external pin include output voltage, soft-start time, non-latching over current protection, and selectable spread spectrum frequency modulation. Other features include enable function, power good indicator, and input under voltage locked-out capability.

The low profile and compact size package  $(6.0 \, \text{mm} \times 6.0 \, \text{mm} \times 3.5 \, \text{mm})$  is suitable for automated assembly by standard surface mount equipment. The wettable flank packaging is available. The uPOL module is Pb-free and RoHS compliance.

#### **APPLICATIONS:**

- Automotive LED Lighting

- Instrument Cluster

- ADAS

- Infotainment

- USB Power Chargers

### **TYPICAL APPLICATION CIRCUIT & PACKAGE SIZE:**

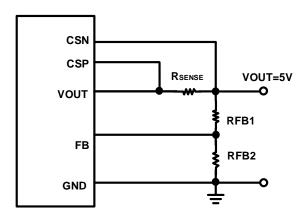

FIGURE.1 TYPICAL APPLICATION CIRCUIT

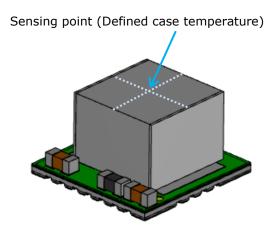

FIGURE.2 HIGH DENSITY uPOL MODULE

1 Rev. 02

# **ORDER INFORMATION:**

| Part Number  | Ambient Temp. Range<br>(°C) | Package<br>(Pb-Free) | MSL     | Note |

|--------------|-----------------------------|----------------------|---------|------|

| VUN12AD03-KM | -40 ~ +125                  | QFN                  | Level 2 | -    |

| Order Code   | Packing       | Quantity |

|--------------|---------------|----------|

| VUN12AD03-KM | Tape and reel | 1000     |

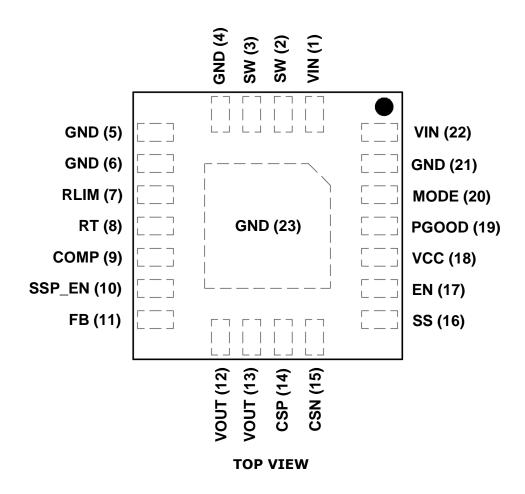

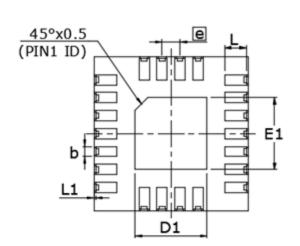

# **PIN CONFIGURATION:**

# **PIN CONFIGURATION:**

| Symbol | Pin No.            | Description                                                             |  |

|--------|--------------------|-------------------------------------------------------------------------|--|

| VIN    | 1, 22              | Power input pin.                                                        |  |

| SW     | 2, 3               | Switch node.                                                            |  |

| GND    | 4, 5, 6, 21,<br>23 | Power ground.                                                           |  |

| RLIM   | 7                  | Current limit setup pin.                                                |  |

| RT     | 8                  | Switching frequency 430kHz with 120kohm setting                         |  |

| COMP   | 9                  | Compensation node.                                                      |  |

| CCD EN | 10                 | Spread spectrum enable input. Connect this pin to VCC to enable         |  |

| SSP_EN | 10                 | spread spectrum. Connect to ground to disable spread spectrum.          |  |

| FB     | 11                 | Feedback voltage input.                                                 |  |

| VOUT   | 12, 13             | Power output pin.                                                       |  |

| CCD    | 14                 | Current sense positive input. The CSP pin should be tied to the CSN     |  |

| CSP    |                    | pin and be left floating if the switch-over function is not needed.     |  |

| CSN    | 15                 | Current sense negative input. The CSN pin should be tied to the         |  |

| CSN    | 15                 | CSP pin and be left floating if the switch-over function is not needed. |  |

| SS     | 16                 | Soft start pin                                                          |  |

| EN     | 17                 | Enable control input. A logic-high enables the converter; a logic-low   |  |

| EN     |                    | disables the device into shutdown mode.                                 |  |

| VCC    | 18                 | Linear regulator output. Add a 10uF, X7R ceramic capacitor from         |  |

| VCC    |                    | VCC to ground.                                                          |  |

| PGOOD  | 19                 | Open-drain power-good indication output.                                |  |

| MODE   | 20                 | Connect this pin to ground to enable power saving mode (PSM).           |  |

| MODE   | 20                 | Connect this pin to VCC to enable force PWM mode (FPWM).                |  |

# **ELECTRICAL SPECIFICATIONS:**

CAUTION: Do not operate at or near absolute maximum rating listed for extended periods of time. This stress may adversely impact product reliability and result in failures not covered by warranty.

| Parameter Description              |                                                       | Min. | Тур. | Max. | Unit |

|------------------------------------|-------------------------------------------------------|------|------|------|------|

| ■ Absolute Maxim                   | Absolute Maximum Ratings                              |      |      |      |      |

| VIN, SW, EN, CSP, CSN              |                                                       | -0.3 | -    | 42   | V    |

| Others                             |                                                       | -0.3 | -    | 6    | V    |

| Tc                                 | Case Temperature of Inductor                          | -40  | -    | +150 | °C   |

| Tj                                 | Junction Temperature, Main IC                         | -40  | -    | +150 | °C   |

| Tstg                               | Storage Temperature                                   | -40  | -    | +150 | °C   |

| ■ Recommendation Operating Ratings |                                                       |      |      |      |      |

| VIN                                | Input Supply Voltage                                  | +4.0 | -    | +36  | V    |

| VOUT                               | Adjusted Output Voltage                               | +0.9 | -    | +8   | V    |

| Ta                                 | Ambient Temperature                                   | -40  | -    | +125 | °C   |

| ■ Thermal Information              |                                                       |      |      |      |      |

| Rth(j <sub>choke</sub> -a)         | Thermal resistance from junction to ambient. (Note 1) | -    | 29.5 | -    | °C/W |

#### NOTES:

<sup>1.</sup> Rth(j<sub>choke</sub>-a) is measured with the component mounted on an effective thermal conductivity test board on 0 LFM condition. The test board size is 30mm×30mm×1.6mm with 4 layers 2oz. The test condition is complied with JEDEC EIJ/JESD 51 Standards.

# **ELECTRICAL SPECIFICATIONS: (Cont.)**

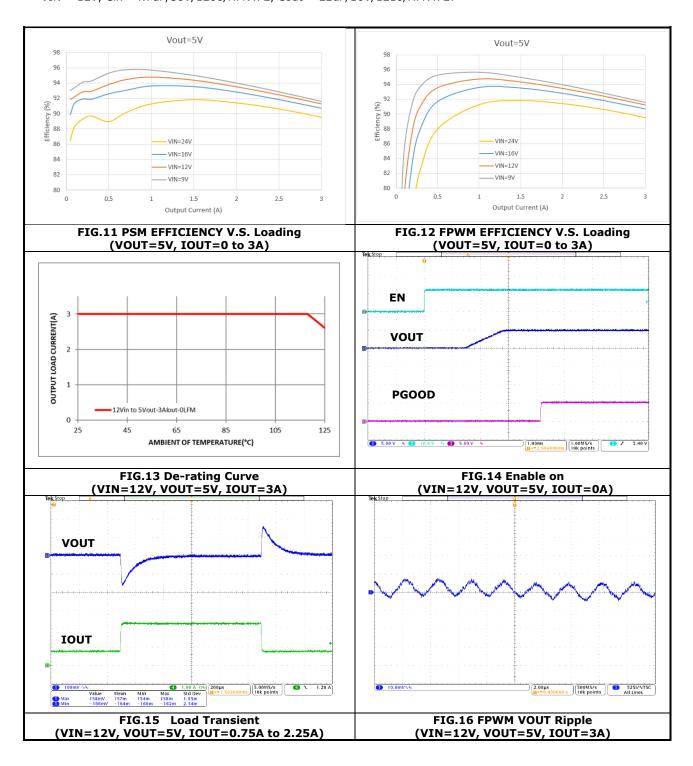

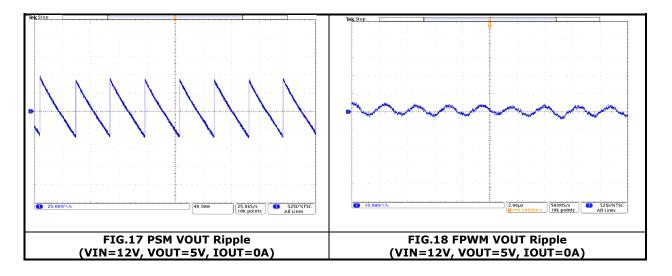

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30 \text{mm} \times 30 \text{mm} \times 1.6 \text{mm}$ , 4 layers 2oz. The output ripple and transient response measurement is short loop probing and 20 MegHz bandwidth limited. VIN = 12V, VOUT = 5V,  $Cin = 4.7 \text{uF}/50 \text{V}/1206/\text{X7R} \times 2$ ,  $Cout = 22 \text{uF}/16 \text{V}/1210/\text{X7R} \times 2$

| Symbol                | Parameter                                  | Conditions                                           | Min.  | Тур. | Max.  | Unit              |

|-----------------------|--------------------------------------------|------------------------------------------------------|-------|------|-------|-------------------|

| ■ Input               | Characteristics                            |                                                      | 1     | •    | •     |                   |

| V <sub>UVLO_TH</sub>  | VIN under<br>voltage lockout<br>threshold  | VIN rising                                           | -     | 3.8  | -     | V                 |

| Vuvlo_th_hy           | VIN under<br>voltage lockout<br>hysteresis |                                                      | -     | 900  | -     | mV                |

| I <sub>S(IN)</sub>    | Shutdown<br>Current                        | VEN=0V                                               | -     | 1.3  | -     | uA                |

| $I_{\mathrm{Q1(IN)}}$ | Quiescent<br>Current                       | VEN=2V, VFB = 0.82V, not switching                   | -     | 37   | -     | uA                |

| I <sub>Q2(IN)</sub>   | Quiescent<br>Current                       | VEN=2V, VOUT=5V, Load=0A, switching, MODE=VCC (FPWM) | -     | 12   | -     | mA                |

| I <sub>Q3(IN)</sub>   | Quiescent<br>Current                       | VEN=2V, VOUT=5V, Load=0A, switching, MODE=GND (PSM)  | -     | 70   | -     | uA                |

| ■ Outp                | ut Characteristic                          | S                                                    |       |      |       |                   |

| $V_{FB}$              | Feedback<br>Voltage                        | T <sub>A</sub> = 25 °C                               | 0.792 | 0.8  | 0.808 | V                 |

| Vsw                   | Switching<br>Frequency                     | RT=120kΩ                                             | -     | 430  | -     | kHz               |

| SS                    | Frequency<br>spread spectrum<br>Range      | Connect SSP_EN pin to VCC                            | -     | 6    | -     | %                 |

| ${ m I}_{\sf LIM}$    | High side switch current limit             | RLIM=39k $\Omega$                                    | -     | 4.72 | -     | А                 |

| D <sub>min</sub>      | Minimum Duty<br>Cycle                      | VOUT/VIN                                             | -     | 4    | -     | %                 |

| $V_{PGLH1\_TH}$       | Power Good                                 | VFB rising, PGOOD low to high                        | -     | 90   | -     | % V <sub>FB</sub> |

| $V_{PGHL1\_TH}$       | Power Good                                 | VFB rising, PGOOD high to low                        | -     | 120  | -     | % V <sub>FB</sub> |

| V <sub>PGHL2_TH</sub> | Power Good                                 | VFB falling, PGOOD high to low                       | -     | 85   | -     | % V <sub>FB</sub> |

| $V_{PGLH2\_TH}$       | Power Good                                 | VFB falling, PGOOD low to high                       | -     | 117  | -     | % V <sub>FB</sub> |

# **ELECTRICAL SPECIFICATIONS: (Cont.)**

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30 \text{mm} \times 30 \text{mm} \times 1.6 \text{mm}$ , 4 layers 2oz. The output ripple and transient response measurement is short loop probing and 20 MegHz bandwidth limited. VIN = 12V, VOUT = 5V,  $Cin = 4.7 \text{uF}/50 \text{V}/1206/\text{X7R} \times 2$ ,  $Cout = 22 \text{uF}/16 \text{V}/1210/\text{X7R} \times 2$

| Symbol               | Parameter                               | Conditions | Min. | Тур. | Max. | Unit         |

|----------------------|-----------------------------------------|------------|------|------|------|--------------|

| ■ Cont               | rol Characteristic                      | S          |      |      |      |              |

| V <sub>EN_TH_R</sub> | Rising threshold voltage                |            | 1.5  | -    | -    | V            |

| V <sub>EN_TH_F</sub> | Falling threshold voltage               |            | -    | -    | 0.8  | V            |

| ■ Fault              | ■ Fault Protection                      |            |      |      |      |              |

| Тотр                 | Over<br>temperature<br>protection       |            | -    | 175  | -    | $^{\circ}$   |

| Тотр_ну              | Over tempeerature protection Hysteresis |            | -    | 15   | -    | $^{\circ}$ C |

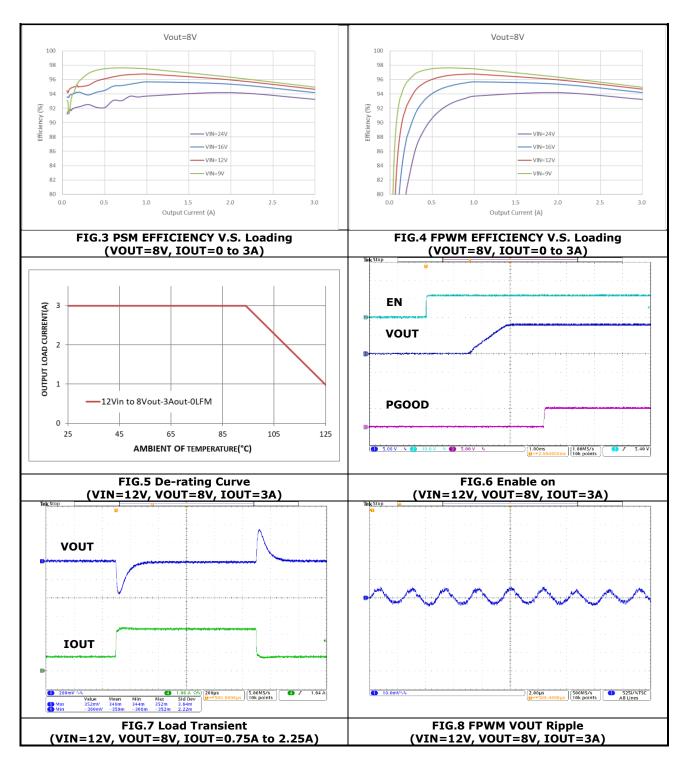

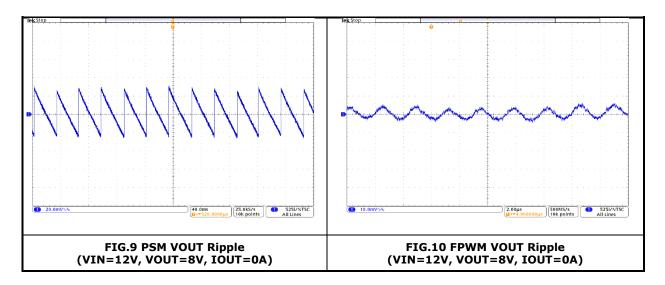

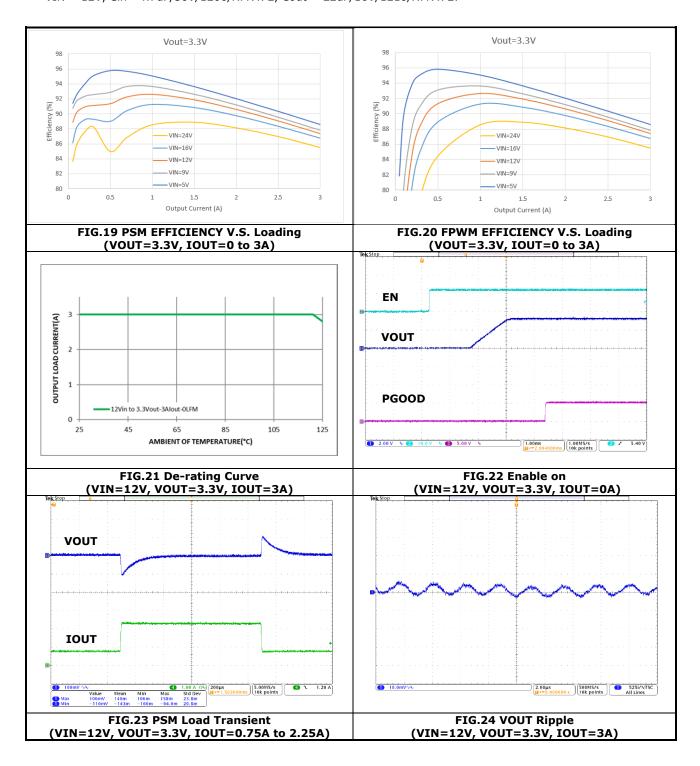

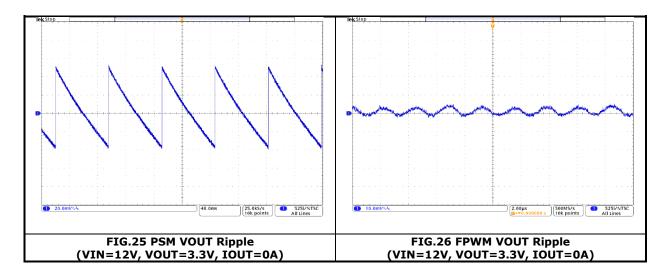

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30mm \times 30mm \times 1.6mm$ , 4 layers 20z. VIN = 12V, Cin =  $4.7uF/50V/1206/X7R \times 2$ , Cout =  $22uF/16V/1210/X7R \times 2$ .

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30 \text{mm} \times 30 \text{mm}$ , 4 layers 2oz. VIN = 12V, Cin =4.7uF/50V/1206/X7R x 2, Cout =  $22 \text{uF}/16 \text{V}/1210/\text{X7R} \times 2$ .

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30mm \times 30mm \times 1.6mm$ , 4 layers 20z. VIN = 12V, Cin =  $4.7uF/50V/1206/X7R \times 2$ , Cout =  $22uF/16V/1210/X7R \times 2$ .

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30 \text{mm} \times 30 \text{mm}$ , 4 layers 2oz. VIN = 12V, Cin =4.7uF/50V/1206/X7R x 2, Cout =  $22 \text{uF}/16 \text{V}/1210/\text{X7R} \times 2$ .

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30mm \times 30mm$ , 4 layers 2oz. VIN = 12V, Cin =4.7uF/50V/1206/X7R x 2, Cout =  $22uF/16V/1210/X7R \times 2$ .

Conditions:  $T_A = 25$  °C, unless otherwise specified. Test Board Information:  $30 \text{mm} \times 30 \text{mm}$ , 4 layers 2oz. VIN = 12V, Cin =4.7uF/50V/1206/X7R x 2, Cout =  $22 \text{uF}/16 \text{V}/1210/\text{X7R} \times 2$ .

# **APPLICATIONS INFORMATION:**

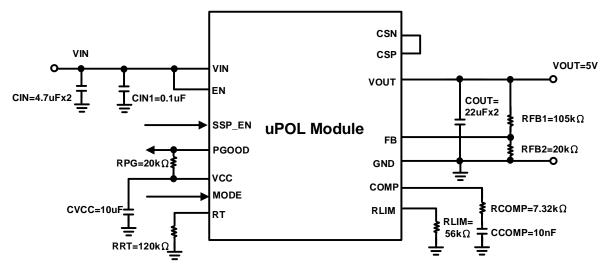

**Reference Circuit for General Application:**

FIG.27 VOUT=5V

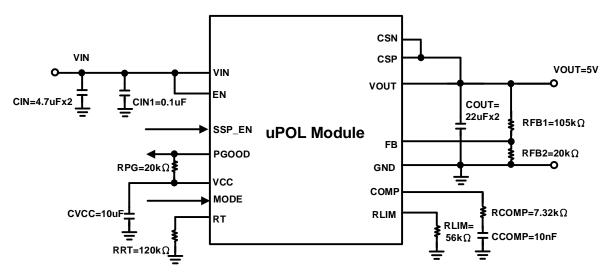

FIG.28 VOUT=5V with Switch-Over Function ( for VOUT = 5V only)

13 Rev. 02

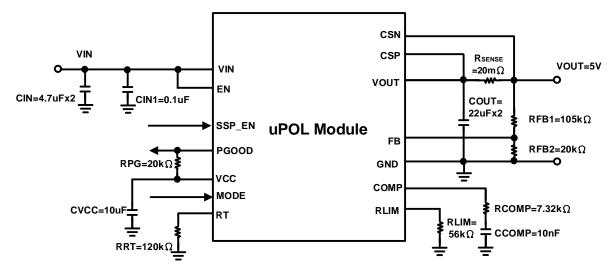

FIG.29 VOUT=5V with Cable Drop Compensation ( for VOUT = 5V only)

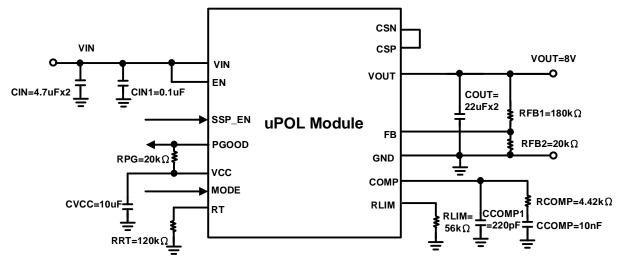

FIG.30 VOUT=8V

#### **Output Voltage Setting:**

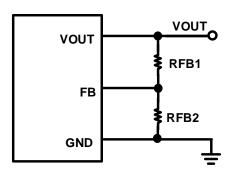

The output voltage can be set by a resistive divider from the output to ground. The resistive divider allows the FB pin to sense a fraction of the output voltage as following figure. The output voltage is set according to the following equation where the reference voltage VFB is typical 0.8V.

$$V_{OUT} = (1 + \frac{RFB1}{RFB2}) \times V_{FB}$$

FIG.31 Output Voltage Setting

#### **Minimum Duty Cycle:**

The module has the limitation for the minimum duty cycle (Duty\_min) 4%, For example, when VOUT is set to 1V, the maximum VIN is 25V.

VIN maximum =

$$\frac{\text{VOUT}}{\text{Duty\_min}}$$

#### **Current Limit Setting**

The current limit of high-side MOSFET switch is adjustable by an external resistor connected to the RLIM pin. The recommended resistor value is  $39k\Omega$  (for typ.4.72A). When the inductor current reaches the current limit threshold, the COMP voltage will be clamped to limit the inductor current. Inductor current ripple also should be considered into current limit setting. The current limit value is set according to the following approximate equation:

$$R_{LIM}(k\Omega) = \frac{178.8}{I_{LIM} - 0.2531} - 1$$

#### **Internal Regulator and Switch-Over**

The module integrates a 5V linear regulator (VCC) that is supplied by VIN and provides power to the internal circuitry. The internal regulator operates in low dropout mode when VIN is below 5V. The VCC can be used as the PGOOD pull-up supply but it is "NOT" allowed to power other device or circuitry. The module implements switch-over function to improve efficiency at all loads. The switch-over function can be enabled when CSP and CSN pins are tied to a voltage higher than 4.8V (typically) and VCC will be supplied from VCSP, otherwise VCC will be supplied from VIN by internal regulator. Typically, the CSP and CSN pins can be tied to the output of the module if the output voltage is regulated at 4.8V to 6V, or can be tied to an external power supply that voltage range is 4.8V to 6V. If the VCSP drops below 4.6V (typically), the internal VCC regulator will automatically turn on to provide power to the internal circuit blocks. The CSP pin should be tied to the CSN pin and be left floating if the switch-over function is not needed.

#### **Power-Good Output**

The PGOOD pin is an open-drain power-good indication output and is to be connected to an voltage source through a pull-up resistor. The external voltage source must be below 5.5V or use internal VCC. It is recommended to connect a  $20k\Omega$  between external voltage source and PGOOD pin.

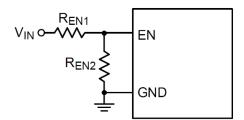

#### **EN Pin for Start-Up and Shutdown Operation**

For automatic start-up, the EN pin, with high-voltage rating, can be connected to the input supply VIN directly. The large built-in hysteresis band makes the EN pin useful for simple delay and timing circuits. The EN pin can be externally connected to VIN by adding a resistor REN and a capacitor CEN, to have an additional delay. The time delay can be calculated with the EN's internal threshold, at which switching operation begins (typically 1.25V). To prevent the device being enabled when VIN is smaller than the VOUT target level or some other desired voltage level, a resistive divider (REN1 and REN2) can be used to externally set the input under-voltage lockout threshold, as following figure.

FIG.32 Resistive Divider for Under-Voltage Lockout Threshold Setting

#### Soft-Start

There is a 10nF capacitor inside the module for soft-start. In normal condition, just keep SS pin floating. The external capacitor CSS between SS pin and GND can increase the soft-start time. An internal current source Iss (6uA) charges an SS pin capacitor to build a soft-start ramp voltage. The FB voltage will track the internal ramp voltage during soft start interval. The typical soft start time which is VOUT rise from zero to 90% of setting value is calculated as following equation:

$$T_{SS}(S) = \frac{0.8}{I_{SS}} \times (C_{SS_{external}} + 10n)$$

#### **Output Under-Voltage Protection**

The module includes output under-voltage protection against over-load or short-circuited condition by constantly monitoring the feedback voltage VFB. If VFB drops below the under-voltage protection threshold (typically 50% of the internal reference voltage), the module will turn off the switches then the inductor current drop to zero and enter the hiccup mode to discharge the CSS. During hiccup mode, the device remains shut down. After the SS pin voltage discharges to less than 150mV (typically), the module attempts to re-start up again.

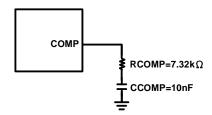

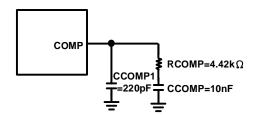

#### **Compensation Network**

The purpose of loop compensation is to ensure stable operation while maximizing the dynamic performance. An undercompensated system may result in unstable operations. For Vout=0.9V~6V application, follow the Fig.33 compensation network. For VOUT=6V~8V application, follow Fig.34 compensation network.

FIG.33 VOUT=0.9V~6V Compensation Network

FIG.34 VOUT=6V~8V Compensation Network

17 Rev. 02

#### **Output Cable Drop Compensation**

The module provides cable drop compensation function, the desired compensation voltage which is set at rated output current can be calculated as below, follow Fig.35 VOUT=5V Cable Drop Compensation Setting.

$$Vdrop = V_{O\_OFFSET} = 21 \times (R_{SENSE} \times I_{OUT} - 0.00476) \times 10^{-6} \times RFB1$$

FIG.35 VOUT=5V Cable Drop Compensation Setting

The RSENSE selection is suggested between  $5m\Omega$  and  $30m\Omega$  to minimize power consumption and must also be selected with an appropriate power rating. Note that the RSENSE should be connected as close to the CSP and CSN pins with short, direct traces, creating Kelvin connection to ensure that noise and current sense voltage errors do not corrupt the differential current sense signals between the CS and VOUT pins. The cable drop compensation function is recommended to operate with CSP and CSN voltages range from 3.3 V to 6V. The RFB1 values can be calculated based on above equation. Choose RFB1 and RFB2 to program the output voltage, the maximum resistance value of RFB2 is  $100k\Omega$ .

# **APPLICATIONS INFORMATION:**

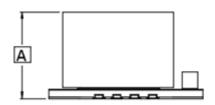

#### **Thermal Considerations:**

All of thermal testing condition is complied with JEDEC EIJ/JESD 51 Standards. Therefore, the test board size is  $30 \text{mm} \times 30 \text{mm} \times 1.6 \text{mm}$  with 4 layers. The case temperature of module sensing point is shown as following figure. Then  $Rth(j_{choke}-a)$  is measured with the component mounted on an effective thermal conductivity test board on 0 LFM condition. The module is designed for using when the case temperature is below 140°C regardless the change of output current, input/output voltage or ambient temperature.

FIG 36. Case Temperature Sensing Point

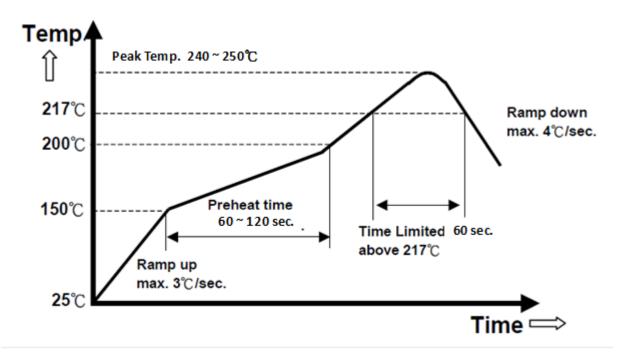

#### **REFLOW PARAMETERS:**

Lead-free soldering process is a standard of electronic products production. Solder alloys like Sn/Ag, Sn/Ag/Cu and Sn/Ag/Bi are used extensively to replace the traditional Sn/Pb alloy. Sn/Ag/Cu alloy (SAC) is recommended for this power module process. In the SAC alloy series, SAC305 is a very popular solder alloy containing 3% Ag and 0.5% Cu and easy to obtain. Following figure shows an example of the reflow profile diagram. Typically, the profile has three stages. During the initial stage from room temperature to 150°C, the ramp rate of temperature should not be more than 3°C/sec. The soak zone then occurs from 150°C to 200°C and should last for 60 to 120 seconds. Finally, keep at over 217°C for 60 seconds limit to melt the solder and make the peak temperature at the range from 240°C to 250°C. It is noted that the time of peak temperature should depend on the mass of the PCB board. The reflow profile is usually supported by the solder vendor and one should adopt it for optimization according to various solder type and various manufacturers' formulae.

FIG.37 Recommendation Reflow Profile

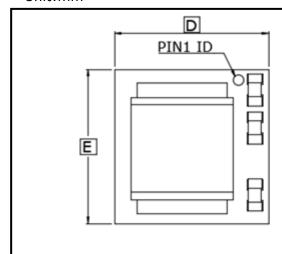

# **PACKAGE OUTLINE DRAW:**

# Unit:mm

| ОТМ | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN         | NOM  | MAX  |  |

| Α   | -           | 3.30 | 3.50 |  |

| D   | 5.90        | 6.00 | 6.10 |  |

| D1  | 2.70        | 2.80 | 2.90 |  |

| Е   | 5.90        | 6.00 | 6.10 |  |

| E1  | 2.70        | 2.80 | 2.90 |  |

| е   | 0.60        | 0.70 | 0.80 |  |

| b   | 0.30        | 0.40 | 0.50 |  |

| L   | 0.70        | 0.80 | 0.90 |  |

| L1  | 0.00        | 0.10 | 0.20 |  |

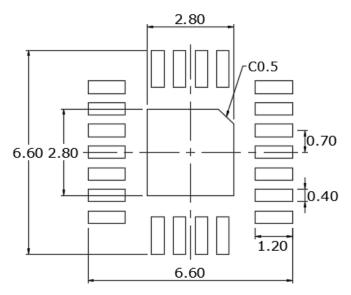

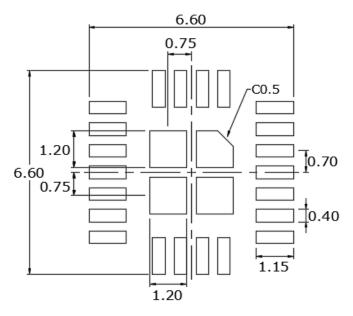

# **LAND PATTERN REFERENCE:**

RECOMMENDED LAND PATTERN

RECOMMENDED STENCIL PATTERN

BASED ON 0.1mm THICKNESS STENCIL(Reference only)

(Recommended solder paste coverage 55~100%)

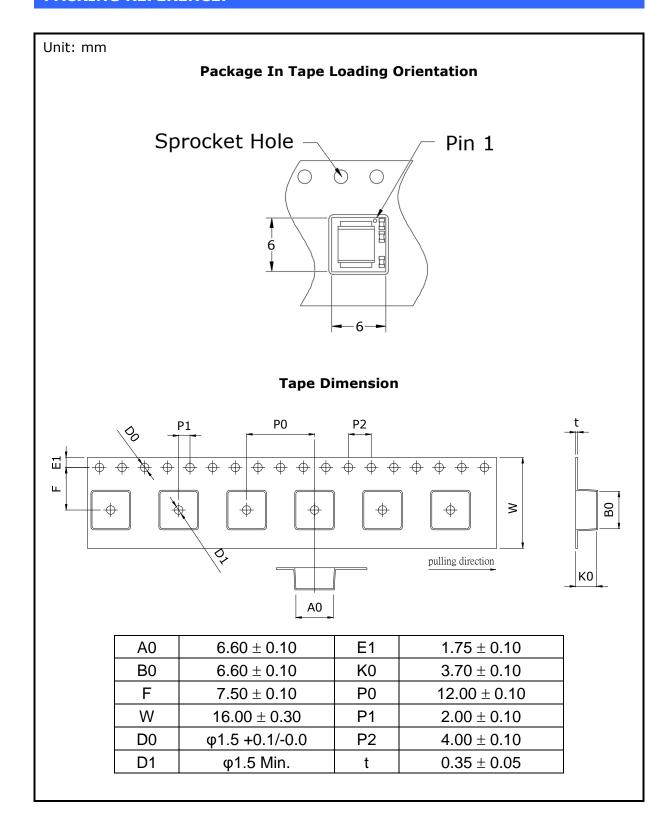

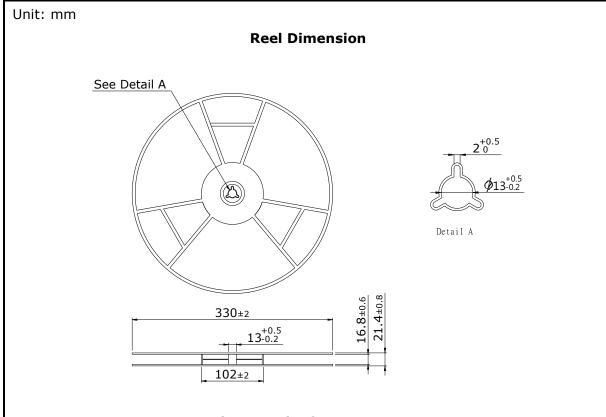

# **PACKING REFERENCE:**

# **PACKING REFERENCE: (Cont.)**

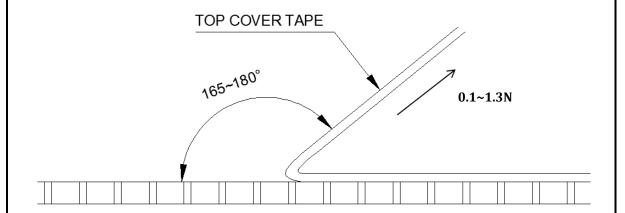

# **Peel Strength of Top Cover Tape**

The peel speed shall be about 300mm/min.

The peel force of top cover tape shall between 0.1N to 1.3N

# **REVISION HISTORY**

| Date       | Revision | Changes                                                |

|------------|----------|--------------------------------------------------------|

| 2019.11.04 | P00      | Release the preliminary spec                           |

| 2020.09.15 | 00       | Release the spec                                       |

| 2020.10.20 | 01       | Add Vout=8V test condition performance characteristics |

| 2020.12.18 | 02       | Update module outline picture                          |

25 Rev. 02